AscenKorea Inc. GPS Module Application Notes

Revision: A10

Reference layout, design tips, guides, and cautions for AscenKorea GPS modules.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc.

Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea.inc. All right reserved

# 2

# Version History

| Subtitle:<br>Doc Type: | GPS Module<br>Technical Doc | ument  |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision               | Date                        | Editor | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A00                    | 2009-05-06                  | Gavin  | First Release                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A01                    | 2009-07-17                  | Gavin  | Add AKS6B (Fully pin compatible<br>with AKS6)                                                                                                                                                                                                                                                                                                                                                                                                   |

| A02                    | 2009-09-04                  | Gavin  | Add VBAKUP and Layout guideline<br>description<br>Change some description about content.<br>Add Appendix page.                                                                                                                                                                                                                                                                                                                                  |

| A03                    | 2010-06-15                  | Brian  | Page 10. AKS6X GPS module design<br>restriction<br>Page 23. Add AKS6E reference design<br>Page 26. Add AKMU1 reference design                                                                                                                                                                                                                                                                                                                   |

| A04                    | 2010-08-27                  | Eric   | Template Update<br>Introduction Update (+ AKM & AKS)<br>Add 2.2.4 Damping Resistor<br>Add 2.2.5 Ground Segmentation<br>Add 2.2.6 Ground Plane                                                                                                                                                                                                                                                                                                   |

| A05                    | 2010-11-04                  | Gavin  | <ol> <li>Phased out product related reference<br/>design removed</li> <li>Add AKSU1LP reference design<br/>(New Product)</li> <li>Add : 2.1.3 UART 0 (RX/TX) –serial<br/>Interface notice items</li> <li>Add : 2.1.6 1PPS- electronic<br/>characteristic description</li> <li>Add Appendix page<br/>III UART to RS232 Interface<br/>IV:UART to USB Interface</li> <li>V: How to extend efficiently the<br/>transfer distance of 1PPS</li> </ol> |

| A06                    | 2010-12-27                  | Eric   | <ol> <li>Note on Antenna Power Supply (p.11</li> <li>Note on Ground Plane (p.16)</li> <li>Add schematics of external antenna<br/>short circuit protection for AKMU1<br/>(p.29)</li> <li>Note on Paste Mask (p.31)</li> <li>Appendix VI:<br/>Add Evaluation Kit (Ev-Kit) schematic<br/>for popular models (p.45)</li> </ol>                                                                                                                      |

| A07 | 2011-03-23 | Gavin  | <ol> <li>Change company contact information</li> <li>Add active antenna detect circuit<br/>reference design of for AKM<br/>U1(p.31)</li> <li>Add AKMU5LP reference design</li> </ol>                                                                                                                                                            |

|-----|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A08 | 2011-05-06 | Gavin  | <ol> <li>Add AKMU5J reference design</li> <li>Eliminate AKML1 (EOL), AKS5 (EOL)<br/>PA6(EOL)</li> <li>Add AKS6E and AKSU1LP about<br/>Antenna Switch query reference<br/>design</li> <li>Add Appendix page:<br/>Cautions on Reflow Soldering<br/>Process</li> <li>Add Trace Tool Information on<br/>Appendix II: 500hm matching line</li> </ol> |

| A09 | 2011-08-09 | Delano | Add :The Pin29 and Pin30 are the bottom ground pads(p.46)                                                                                                                                                                                                                                                                                       |

| A10 | 2012-05-17 | Delano | Over Current Protection LDO modify<br>Over Current Protection Circuit(p.30)                                                                                                                                                                                                                                                                     |

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

Rm. 710, 7F, Halla Sigma Velley B/D. Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

AscenKorea Inc.

copyright ⓒ AscenKorea Inc. All right reserved

# Table of Contents

| 2.1 Circuit Design       7         2.1.1 Power supply Vcc       7         2.1.2 VBACKUP (BACKUP_PWR) backup battery       8         2.1.3 UART 0 (RX/TX) –Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. General Rules for Design-in       7         2.1 Circuit Design       7         2.1.1 Power supply Vcc       7         2.1.2 VBACKUP (BACKUP_PWR) backup battery       8         2.1.3 UART 0 (RX/TX) –Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17 |

| 2.1 Circuit Design       7         2.1.1 Power supply Vcc       7         2.1.2 VBACKUP (BACKUP_PWR) backup battery       8         2.1.3 UART 0 (RX/TX) –Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                |

| 2.1 Circuit Design       7         2.1.1 Power supply Vcc       7         2.1.2 VBACKUP (BACKUP_PWR) backup battery       8         2.1.3 UART 0 (RX/TX) –Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                |

| 2.1.2 VBACKUP (BACKUP_PWR) backup battery       8         2.1.3 UART 0 (RX/TX) -Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                          |

| 2.1.2 VBACKUP (BACKUP_PWR) backup battery       8         2.1.3 UART 0 (RX/TX) -Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                          |

| 2.1.3 UART 0 (RX/TX) -Serial Interface       10         2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                    |

| 2.1.4 GND-Ground       10         2.1.5 Antenna Design       11         2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                            |

| 2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                    |

| 2.1.6 1PPS Signal       13         2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                    |

| 2.1.7 Design Restriction       14         2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                                                       |

| 2.2 Layout Guideline       15         2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2.1 Clearance       15         2.2.2 Placement       15         2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.3 Trace       16         2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.2.4 Damping Resistors       16         2.2.5 Ground Segmentation       17         2.2.6 Ground Plane       17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2.5 Ground Segmentation 17<br>2.2.6 Ground Plane 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2.5 Ground Segmentation 17<br>2.2.6 Ground Plane 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2.6 Ground Plane 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3. Reference Design and Noice 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1 AKML3 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2 AKS220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3 AKS422                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.4 AKS6B/AKS6E 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.5 AKMU1 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.6 AKSU1LP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.7 AKMU5LP 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.8 AKMU5J 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4. Thermal Profile for SMD Modules 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5. Troubleshooting 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6. Contact 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Appendix I: Super Capacitor Design 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Appendix II: About 50 ohm Matching Line 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Appendix III: UART to RS232 Interface 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Appendix IV: UART to USB Interface 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Appendix V: How to efficiently transfer 1PPS through extended distances 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Appendix VI: Evaluation Kit (EV-KIT) Schematics53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix VII: Cautions on Reflow Soldering Process57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

Ascenkorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © Ascenkorea Inc. All right reserved

# **Attention**

Please read carefully before you start:

- Global Positioning System (GPS) is the property of American Ministry of National Defense, and they held full responsibilities in regard to the preciseness and the maintenance of the entire system. Any changes they have made may have significant impacts on the capabilities and preciseness of GPS.

- If you use GPS receiver inside buildings, tunnels, or besides any huge objects, the GPS signals might be cut-off or disturbed. Please do not assume the receiver has malfunctioned.

- This application note provides the necessary guideline to successfully design a system using GPS modules. For detailed module specification, please refer to the corresponding datasheet of GPS module.

- GPS Module is an electrostatic sensitive device, please don't touch GPS module directly, please follow ESD safety rule when handling.

- For the first time, it is strongly recommended to bring the device, using GPS module, outdoor with under open sky for at least 10 to 15 minutes to ensure 3D position fix and almanac update.

6

# **Technical Support**

If you have any technical problems or cannot find the required information in our documents, please feel free to contact us for technical support. Below is a list of information which you can provide that will be very useful to us in determining source of the problem and the necessary solution:

- 1. Your company name and website

- 2. Description about application and system

- 3. GPS module type

- 4. GPS firmware version

5. Description of the question or problems encountered, together with pictures or videos files

- Test setup

- The problem or issue shown in pictures

Technical contact information: sales@ascen.co.kr

# 1. Introduction

AscenKorea has a variety of GPS modules designed for many different applications. The modules are classified into two major families: AKMLx and its successor the AKMxx family, or the AKSx and its successor the AKSxx family (where x denotes the model number). The major difference between these two families is the inclusion of smart patch antenna. AKS come with the ceramic antenna, while AKM do not. These GPS modules provide a complete GPS solution that excels in position, speed, and accuracy performances as well as high in sensitivity and tracking capabilities in urban environment. The GPS module are powered by MediaTek Inc. GPS chipset, the world's leading digital media solution provider and largest fab-less IC Company in Korea. AscenKorea's GPS solutions are suitable for assortment of devices, even small-form-factor ones.

# 2. General Rules for Design-in

In order to obtain good GPS performances, there are some rules which require attentions for using GPS module:

In order to obtain good GPS performances, there are some rules which require attentions for using GPS module:

# 2.1 Circuit Design

### 2.1.1 Power supply Vcc

It is necessary to provide a clean and stable power supply for our GPS module in order to obtain good performances (Ex: TTFF). Unstable power source will have a significant negative impact on the GPS performance. To achieve this, the Vcc ripple must be controlled under 50mVpp. In addition, there are also some important suggestions for main power circuit design:

- Add ferrite bead, power choke or low pass filter for power noise reduction

- Use linear regulator for voltage regulation

- Use enough decoupling capacitors for stable voltage due to current variation.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

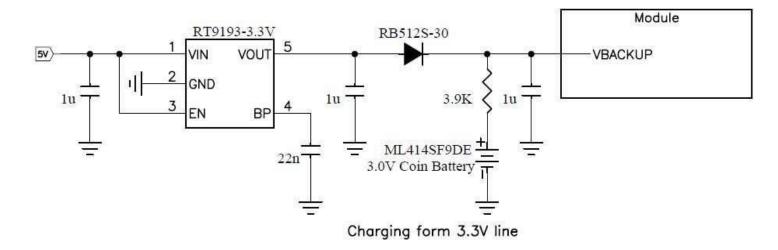

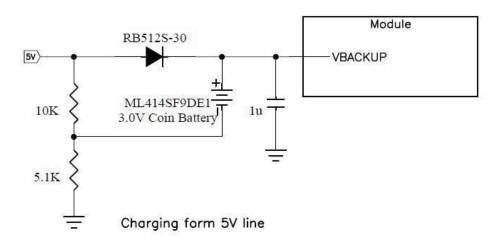

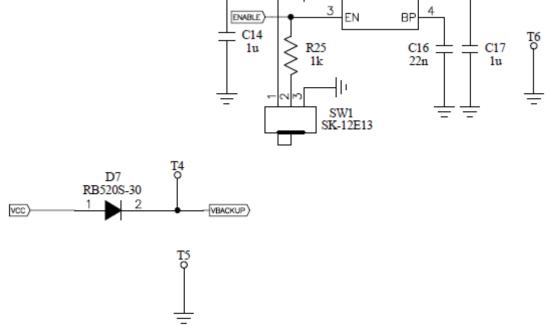

#### 2.1.2 VBACKUP (BACKUP\_PWR) backup battery

The backup power is necessary for all modules to work normally.

Backup power is used for keeping RTC running and navigation data after the main power was turn off. For most cases with backup power, the GPS module can have a shorter TTFF, Time to First Fix, or hot start.

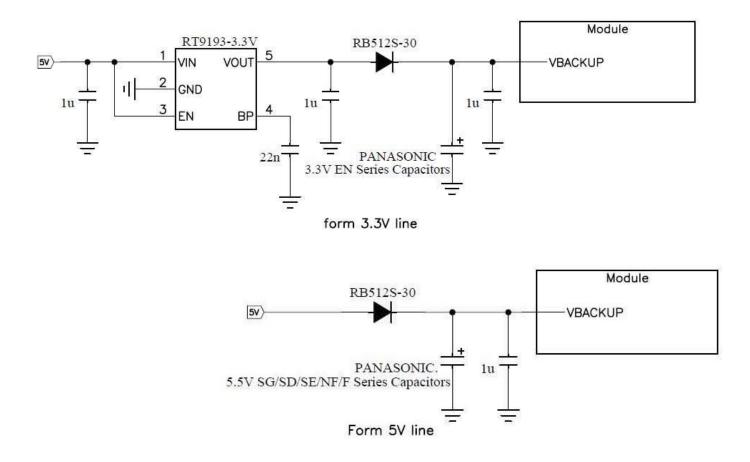

It is recommended to connect the module via VBACKUP to a sustained power source (ex: Li-Ion rechargeable coin battery) for backup power. There are several ways to maintain the backup power, such as Li battery, super capacitor or just wired to VCC. See figure 1, 2 and 3 for reference. About super capacitor reference design, please refer to appendix.

#### Figure F1, Backup power using regulator for GPS module

Figure F3, Backup power using regulator with super capacitor

# 2.1.3 UART 0 (RX/TX) -Serial Interface

UART is the default interface, the logic, which is TTL level, supports transfer baud rate ranging from 4800 bps to 115200 bps. If RS232 logic-level is needed for any particular application, then the use of level shifter is necessary. Please leave RX open if it is not used as there is an internal pull-up to VCC. Please don't use an external pull-up to prevent unexpected current draw. Please refer to "Appendix III: UART to RS232 Interface" for more information on designing RS232 logic for UART.

Notice:

Please don't connect diode(s) to RX/TX as it will lower signal driving capability which might adversely affect RX/TX signal level (ex. no data output).

# 2.1.4 GND-Ground

Make sure all GND pins of module are linked to a good ground connection.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D. Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright @ AscenKorea Inc. All right reserved

# 2.1.5 Antenna Design

GPS antenna is a receiving device to acquire week GPS signal from sky. Popular solution would be ceramic patch antenna due to its small form factor with low cost. There are two types of antennas, passive and active. Passive antenna is with solely antenna itself. Active antenna is with LNA to have high gain with the cost of current supply.

Antenna can be chosen according to radiation efficiency, radiation pattern, gain, bandwidth, form factor and cost. Make sure the ground plane is sufficient for the antenna to operate with acceptable performance. And place the matching circuit between antenna and GPS module to compensate the frequency shift due to PCB layout.

To optimize the reception performance under an unfavorable operation environment with noisy sources, please consider the use of an additional SAW filter as a possible solution

- The total noise figure, NF, must be under 1.5dB.

- Make sure the antenna is not placed closely to the noisy portion of the whole circuit design.

For the noise rejection of out-of-band, make sure the antenna do NOT have oscillation frequency except the L1 band, 1575.42MHz. For example:

- ✓ 1575.42MHz main frequency source form not GPS source

- 525.14MHz frequency source (525.14 x 3 = 1575.42MHz)

- 315.084MHz frequency (315.084 x5=1575.42 MHz)

- 4.092MHzMHz GPS intermediate frequency

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D. Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

Please also pay special attention to the design of power supply for the external active GPS antennas as they vary between different GPS module models.

- For some GPS modules (ex. AKS6E, AKSU1LP), the DC voltage for the active antenna is provided internally through the same pin as external antenna input pin (EX\_ANT), or through two different pins (ex. AKML1). [Type 1]

- For some models (ex. AKSL3), the power supply for the active antenna needs to be externally provided and is connected to a designated pin (VANT) located on the module, where the DC voltage for the active antenna is outputted from the external antenna input pin. [Type 2]

- Some (ex. AKMU1), the power supply needs to be externally provided and is connected directly to the active antenna. [Type 3]

- AKMU5LP has a unique "Antenna Advisor" System that can be enabled with a additional resistor. Please see reference design for more details. [Type 4]

- AKMU5J comes with special GPS jammer detect feature called "Anti-JACK™" and Antenna Advisor System that requires special attention, please refer to AKMU5J data sheet for more details. [Type 5]

| Module | AKS4 | AKS6E | AKML1        | AKML3 | AKMU1 | AKS<br>U1LP | AKM<br>U5LP  | AKMU5J |

|--------|------|-------|--------------|-------|-------|-------------|--------------|--------|

| IVIOUE |      |       |              |       |       |             |              |        |

| Type 1 |      | ~     | $\checkmark$ |       |       | ~           |              |        |

| Type 2 | ~    |       |              | ~     |       |             |              |        |

| Туре З |      |       |              |       | ~     |             |              |        |

| Type 4 |      |       |              |       |       |             | $\checkmark$ |        |

| Type 5 |      |       |              |       |       |             |              | ~      |

# 2.1.6 1PPS Signal

(Applicable to modules with 1PPS support)

1PPS signal is an output pulse signal useful for timing application, its electronic characteristic are listed below:

Low Voltage level: 0~0.4V, High Voltage level: 2.8~3.1V Source current: 14 mA, Sink current 14 mA

Notice:

Depending on user's application, LED + resistor can be directly used with the 1PPS pin without the need of an external buffer. Please note the reference resistor value is 330 ohm.

Please refer to Appendix V for more information on 1PPS signal transmission.

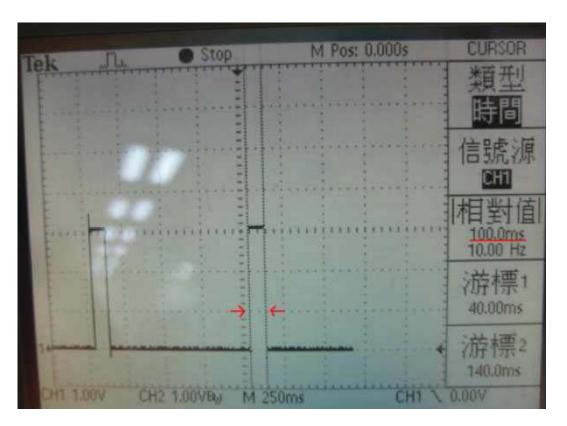

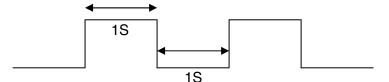

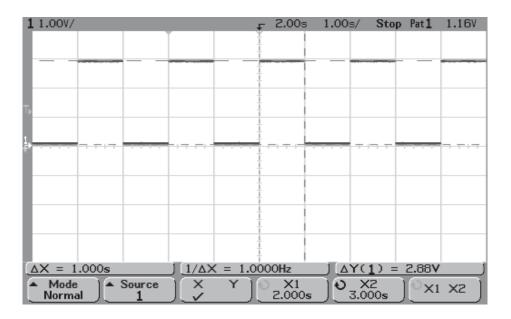

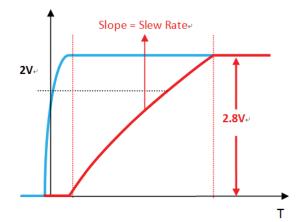

Figure 2.1.6, 1PPS signal and its pulse width with 100ms duration

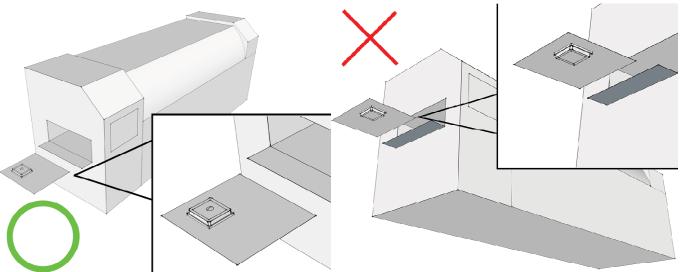

# 2.1.7 Design Restriction

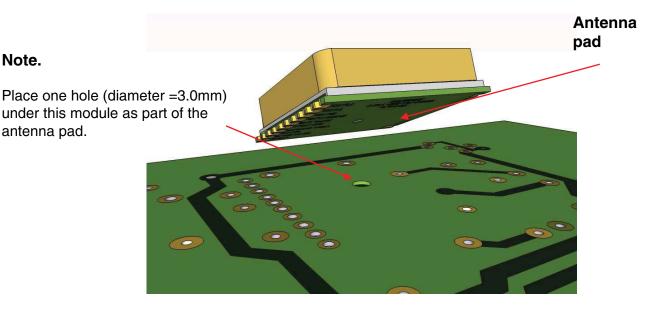

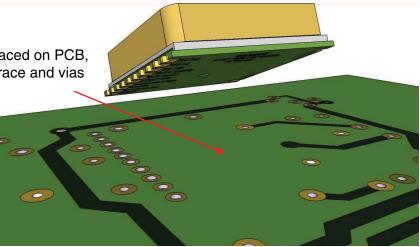

Please keep out of traces and via under the AKS6X/AKSU1LP GPS module to avoid any interferences affecting the antenna pin located at the bottom of the PCB board. (Module AKS6X is used as an example for the figures below)

#### Note.

If the hole can't be placed on PCB, please don't let any trace and vias pass the area.

# 2.2 Layout Guideline

Please follow the layout criteria to design a system using GPS module.

# 2.2.1 Clearance

It is better to place GPS module higher than other circuitry for better reception. There is only patch antenna on top layer, but other components place on bottom layer

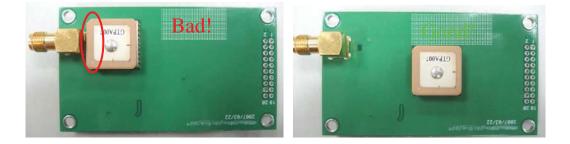

### 2.2.2 Placement

Place the decoupling capacitors close to GPS module Place the damping resistors close to GPS module Do not place GPS module close to high-speed digital processing circuitry Do not place GPS module close to high-current switching power circuitry Do not place GPS module close to clock sources circuitry Do not place patch antenna close to the tall metal object.

# 2.2.3 Trace

Do not trace under the GPS module.

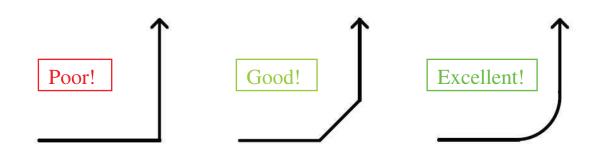

The USB differential signals should be trace close for minimum loop radiation RF traces have to execute the 50 ohm impedance control for good sensitivity Any right angle turn in trace routing should be accomplished with two 135 degree turn or an arc turn

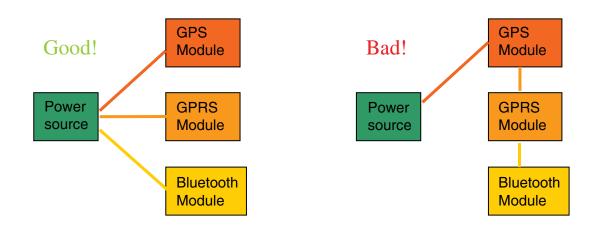

It is better to have independent trace of power source for any device

### 2.2.4 Damping Resistors

The purpose of placing damping resistor at the designated I/O ports (Typically the Rx and Tx) of the GPS module is to limit the radiation given out at these points to comply with FCC or CE regulations. Fine tuning the damping resistor is required as the amount of radiation will be dependent on user's application. As a general rule, the longer the layout line is, the higher the radiation will be, and a higher value (ohm) damping resistor is required to keep the radiation level down.

Typically, Damping Resistor under 1000ohm will not affect communication signal quality.

# 2.2.5 Ground Segmentation

The separation of ground between GPS module and the rest of the system is recommended to avoid interference. If this is not possible, it is best to follow these typical rules: segmentation of ground between digital and analogue system, high current and low current system, and different radiation systems in general (such as GPS and GPRS).

One way to segment the ground is to place digital and noise component at one corner of the board, while placing analog and quiet components at the opposite corner of the board. Make sure there is no crossing of microstrip or current between the two component sets and grounds of each sets are contacted in one point only.

Another way to do this is the place the two different sets at different layers of the board, while the ground of each layer is contacted in one point only (preferable at border of the board).

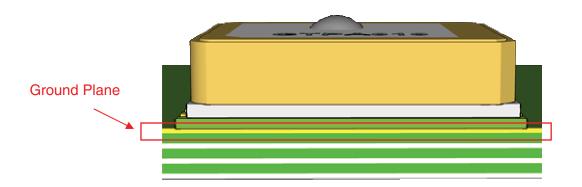

# 2.2.6 Ground Plane

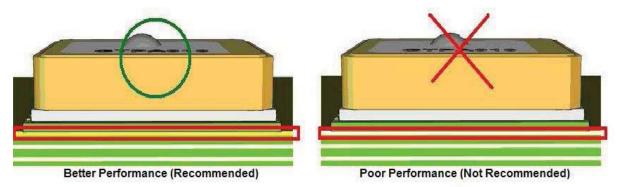

Having a ground plane designed for GPS module with built-in passive antenna (such as AKS6B, AKS6E, AKSU1LP) is crucial as it can enhance the magnetic-field line of the antenna for better GPS signal reception. It is strongly recommended to have a ground plane designed underneath the GPS module with integrated antenna at top layer. The GPS reception can be further improved by increasing ground plane size until it reaches the optimum size for GPS reception (performance equal to an external GPS antenna).

The recommended thickness for the ground layer is 0.5 to 1 OZ (0.0175 to 0.035 mm)

It is best to place the ground plane on the top layer of the PCB, directly underneath the GPS module as the figure below shows:

#### Ground Plane for FR4 Design

Here is a table that shows the ground plane size in relation to C/N value of AKS6 series for reference:

| Ground Plane Area (Length x Width) (cm) | Top 4 satellite C/N values (higher the better) |

|-----------------------------------------|------------------------------------------------|

| No Ground Plane                         | 45, 44                                         |

| 2.6 x 2.6 (Square)                      | 47, 46, 45, 44                                 |

| 3.6 x 3.6 (Square)                      | 48, 46, 46, 44                                 |

| 4.6 x 4.6 (Square)                      | 47, 47, 46, 46                                 |

| 5.6 x 5.6 (Square)                      | 48, 47, 46, 44                                 |

| 6.6 x 6.6 (Square)*                     | 50, 49, 48, 47                                 |

| 2.4 x 3.6 (Rectangle)                   | 48, 46, 46, 46                                 |

| 5.6 x 3.6 (Rectangle)                   | 48, 46, 46, 46                                 |

| 7.6 x 3.6 (Rectangle)*                  | 49, 49, 48, 48                                 |

| 9.6 x 3.6 (Rectangle)                   | 48, 48, 47, 47                                 |

\*C/N performance close to that of an external antenna

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Ila Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-g

Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

copyright 🕝 AscenKorea Inc. All right reserved

# 3. Reference Design and Noice

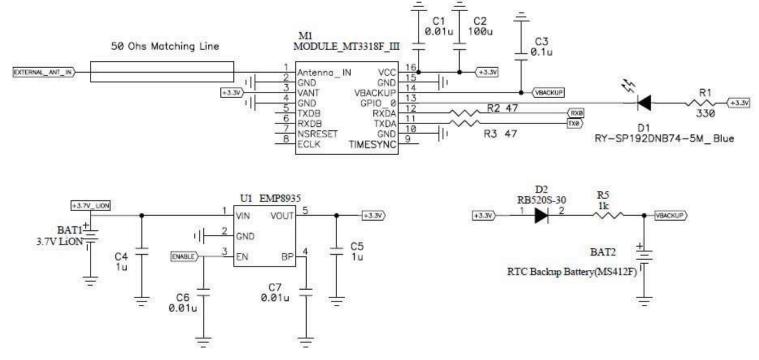

#### 3.1 AKML3

#### Notice about design:

Please note the Vcc and VBAK power source design; it is recommended there are some capacitors and ferrite chip beads.

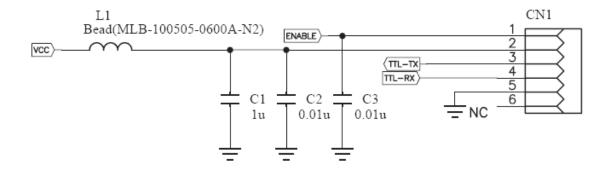

# 3.2 AKS2

# **AKS2-C reference design**

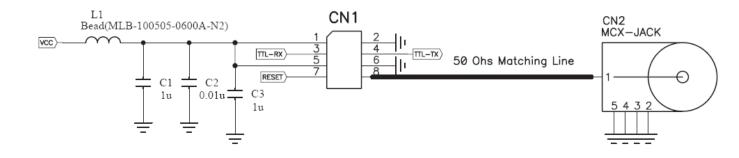

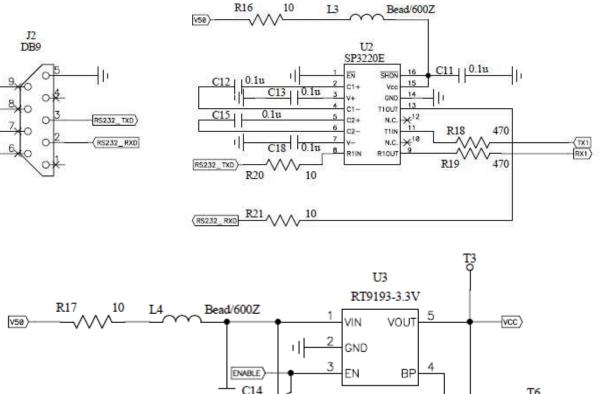

Note: For better filtering L1/C1/C2/C3 components need to be placed Closely CN1

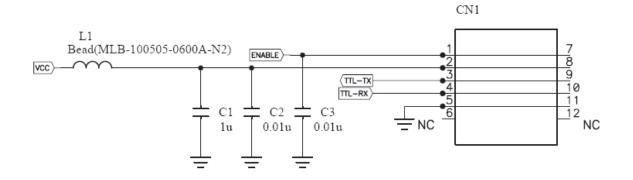

# **AKS2-P** reference design

Note: For better filtering L1/C1/C2/C3 components need to be placed Closely CN1

#### Notice about design:

Please note the Vcc and VBAK power source design; it is recommended there are some capacitors and ferrite chip beads.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea Inc. All right reserved

#### 3.3 AKS4

Note: For better filtering L1/C1/C2/C3 components need to be placed Closely CN1

#### Notice about design:

Please note the Vcc and VBAK power source design; it is recommended there are some capacitors and ferrite chip beads.

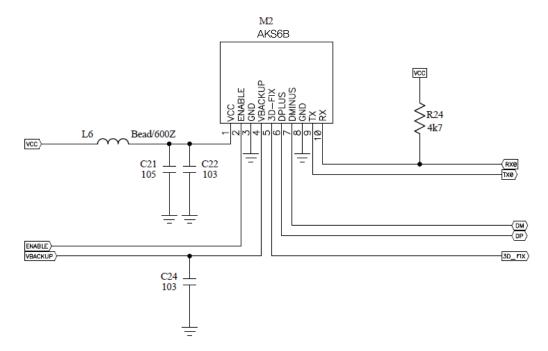

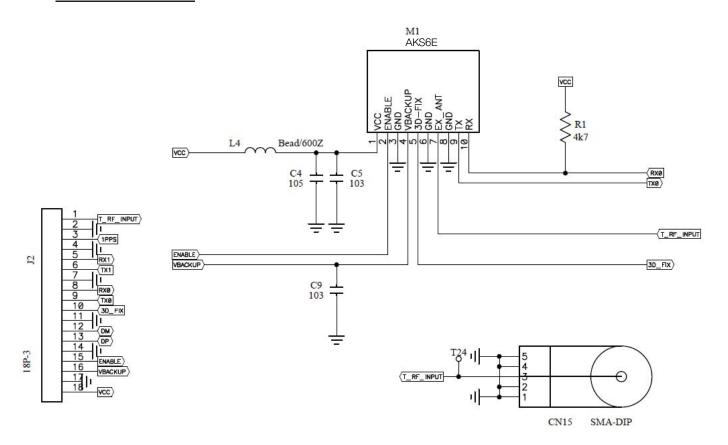

# 3.4 AKS6B/AKS6E

#### AKS6/AKS6B UART reference design

#### AKS6/AKS6B USB reference design

#### AKS6E UART reference design

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea Inc. All right reserved

# Notice about the design:

# ENABLE (Pin2)

Keep open or pull high to Power ON. Pull low to shutdown the module.

Enable (High): 1.8V<= Venable<=VCC

Disable (Low): 0V<= Venable<=0.25V

The pin could be left open if system doesn't want to shut down the power.

#### VBACKUP (Pin4)

This is the power for GPS chipset to keep RTC running when main power is removed. The voltage should be kept between 2.0V and 4.3V. (Typical : 3.0V)

The pin must be connected for normal operation.

#### 3D-FIX (Pin5)

The 3D-FIX was assigned as fix flag output. If not used, keep floating.

#### 2 Before 2D Fix

The pin should continuously output one-second high-level with one-second low-level signal.

#### 3 After 2D or 3D Fix

The pin should continuously output low-level signal.

Low

#### DPLUS (Pin6) (for AKS6/AKS6B)

USB Port DPLUS Signal: if you use the USB interface for connection, please install MT3329 USB VCP driver before you use the module.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 859 7813/ www.AscenKorea.com /sales@ascen.co.kr

#### DMINUS (Pin7) (for AKS6/AKS6B)

USB Port DMINUS Signal: if you use the USB interface for connection, please install MT3329 USB VCP driver before you use the module.

#### EX\_ANT (Pin7) (only for AKS6E)

External Antenna input and Output 3.0V power for external antenna.

The maximum consumption current for the GPS antenna is limited to 30mA.

When a 3mA or higher current is detected, the IC will acknowledge the external antenna as being present and uses external antenna for reception.

In the event of short circuit occurring at external antenna, the module will limit the drawn current to a safe level.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea Inc. All right-reserved

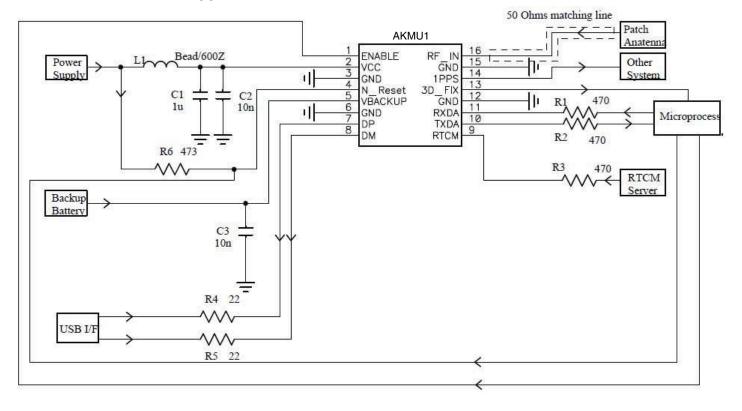

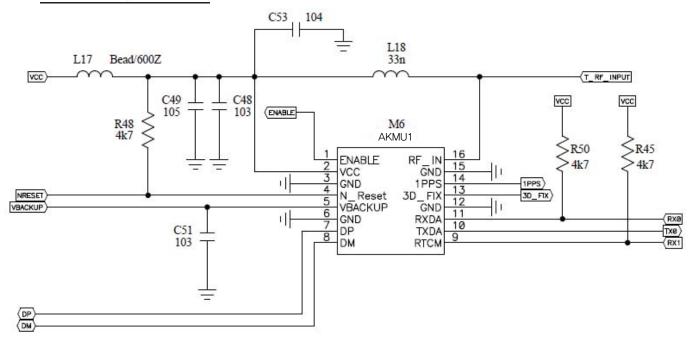

# 3.5 AKMU1

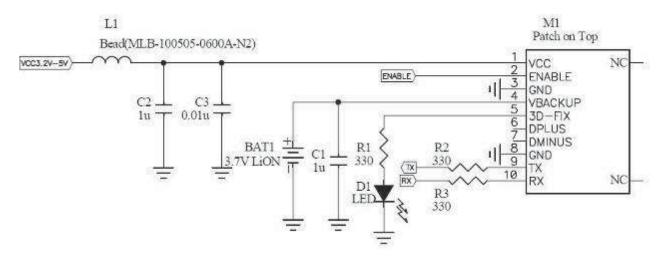

# • Patch Antenna Application

#### Notice:

- 1. Ferrite bead L1 was add for power noise reduction.

- 2. C1 and C2 decoupling capacitor should put near module.

- For C1, the value depends on system noise, range 1uF~100uF is reasonable.

- 3. Damping resistors R1, R2, R3, R4 and R5 should be fine-tuned for system application.

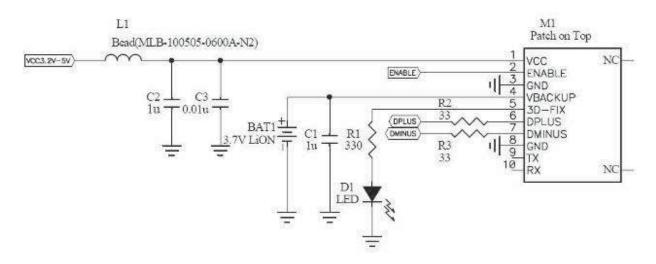

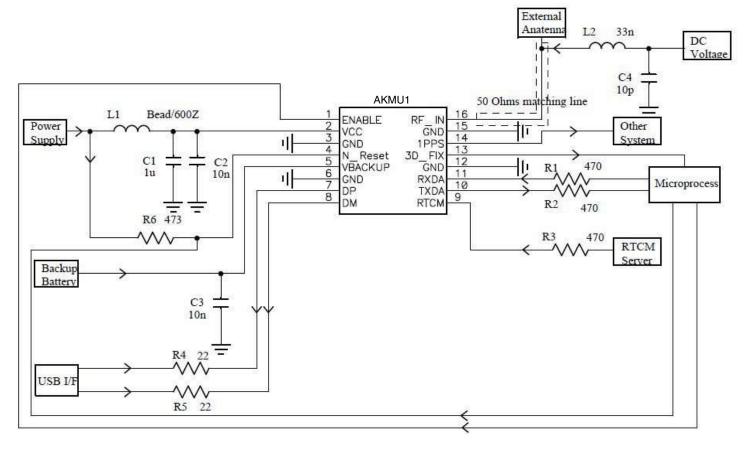

# • External Antenna Application

#### Notice:

- 1. Ferrite bead L1 was add for power noise reduction.

- 2. C1 and C2 decoupling capacitor should put near module.

- For C1, the value depends on system noise, range 1uF~100uF is reasonable.

- 3. Damping resistors R1, R2, R3, R4 and R5 should be fine-tuned for system application.

- 4. L2 was added for RF Choke.

- 5. C4 was added for power noise reduction.

#### RF\_IN (Pin16)

GPS RF signal input. If used to external active antenna, which is the power supply from external DC voltage. The voltage should be kept between 3.0V~10V, **Typical 3.0V**

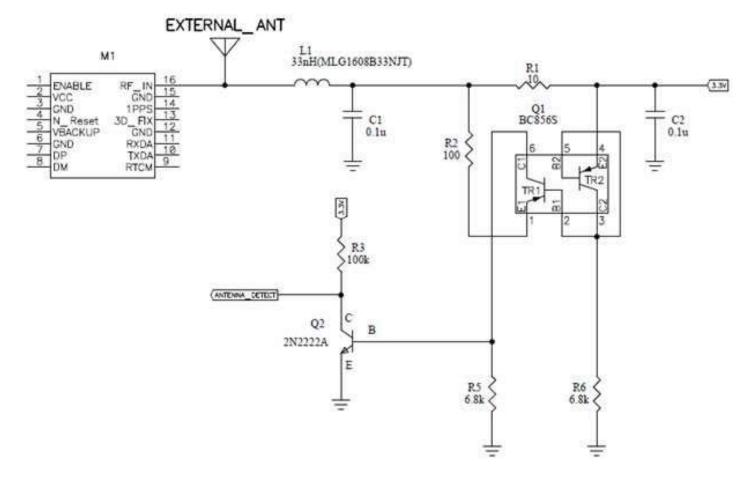

# • Antenna (Active) detect circuit reference design

### Reference Design

Conditions : When ANTENNA \_ DETECT logic  $\cong$  2.0V

| $R_2(\Omega)$ | EXTERNAL_ANT Current<br>(mA) |

|---------------|------------------------------|

| 100           | 3.72                         |

| 200           | 3.02                         |

| 220           | 2.84                         |

| 330           | 1.95                         |

| 390           | 1.46                         |

| 470           | 0.90                         |

| Table         | 4.4                          |

Table 1-1

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

Ascenkorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.Ascenkorea.com /sales@ascen.co.kr copyright © Ascenkorea Inc. All right reserved

#### ANTENNA \_ DETECT Logic

| ANTENNA _ DETECT<br>Logic | EXTERNAL      | Note                                                       |

|---------------------------|---------------|------------------------------------------------------------|

| 1                         | EXTERNAL Load | The consumption current is higher than specified table 1-1 |

| 0                         | No Load       |                                                            |

Table 1-2

**Summary:** 470Ω is the recommended value of R<sub>2</sub> when using this schematic. With the external antenna connected (EXTERNAL Load), if the current of EXTENRNAL\_ANT is 0.9 mA or higher, the output logic of ANTENNA\_DETECT will be 1. If the external antenna is not connected (No Load), the output logic will be 0 for ANTENNA\_DETECT (see Table 1-2 for reference).

The output logic of ANTENNA\_DETECT can be adjusted accordingly by changing the value of R2 to alter for the level of consumption current, please refer to Table 1-1 for more details.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 /813/ www.AscenKorea.com /sales@ascen.co.kr copyright © Ascentform Inc. All right reserved

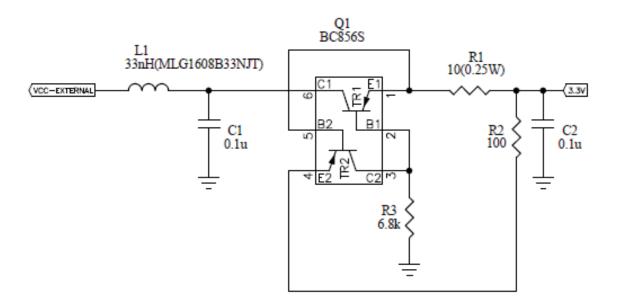

### • Over Current Protection Circuit

Because of AKMU1/AKMU2P's design, the power supply for external active antenna needs to be provided from an outside source without entering the module. For those interested in protecting the External Antenna from short circuit at the external antenna pin, please add an over current protection circuit as below, and place it in between the power source for the external active antenna and the power input of the external active antenna.

#### Note:

#### Normal Action

When the power supply 3.3V input, the TR1 is into saturation region and VCC-EXTERNAL output voltage, TR2 is into cutoff region.

#### **Protect Action**

If the VCC-EXTERNAL is short to ground and the power supply 3.3V input, the TR1 and TR2 is into active region, therefore limit current is R3 determine.

#### R3 value for Limit Current

R3 is 20K the limit current approximately 30mA.

R3 is 6.8K the limit current approximately 50mA.

R3 is 390 the limit current approximately 100mA.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

copyright © AscenKorea Inc. All right reserved

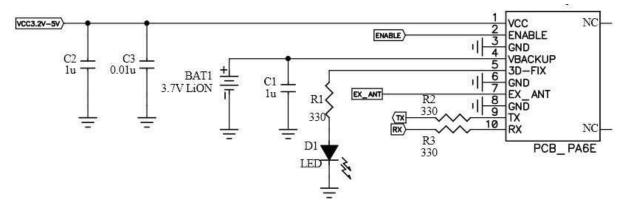

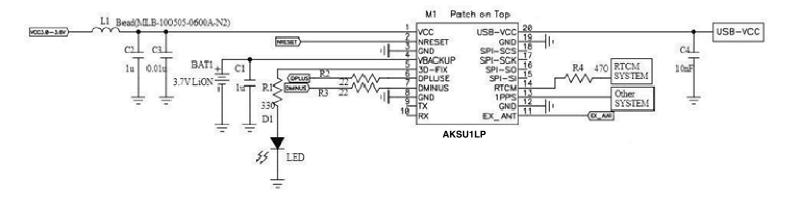

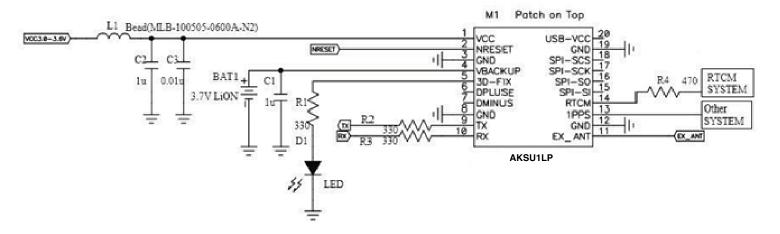

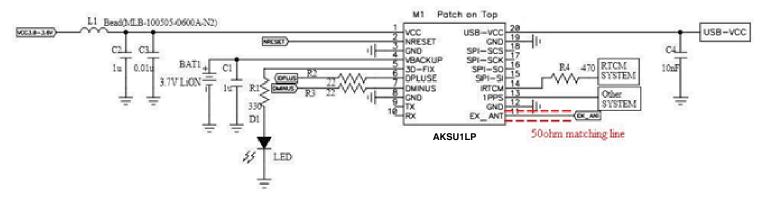

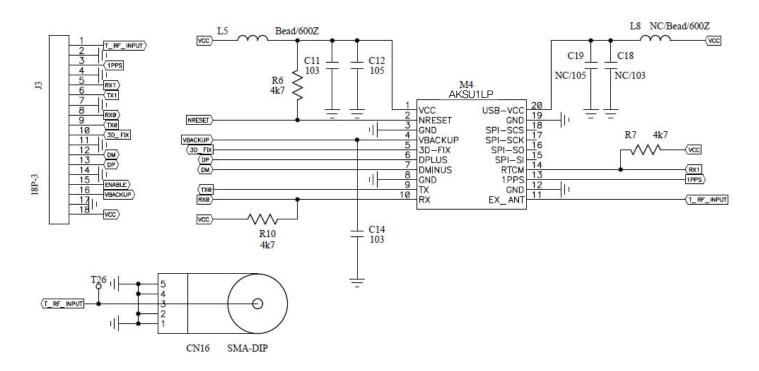

### 3.6 AKSU1LP

#### **USB** Interface

# **UART** Interface

### **Active Antenna Application**

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea Inc. All right reserved

# 3.7 AKMU5LP

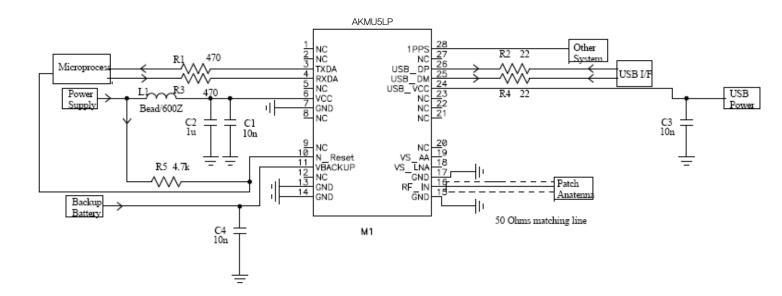

### Patch (Passive) Antenna

When using a passive antenna, please connect the antenna directly to Pin16, RF\_IN.

#### Note:

- 1. Ferrite bead L1 is added for power noise reduction.

- 2. C1, C2, C3, and C4, decoupling capacitor should be put near the module. For C2, the value chosen depends on the amount of system noise, the range from 1uF to 100uF is reasonable.

- 3. Damping resistors R1, R2, R3, R4 and R5 could be modified based on system application.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

copyright © AscenKorea Inc. All right reserved

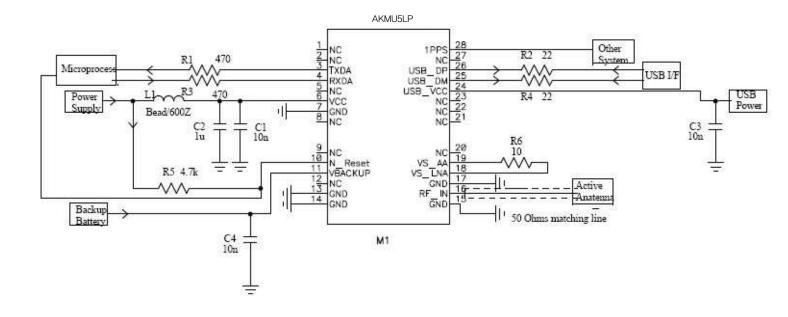

#### Active Antenna with Antenna Advisor

When using an active antenna, a supply voltage is typically required to drive the internal LNA located inside the active antenna. For majority of the active antenna, the power will be sent on the same coaxial cable used for GPS signal reception through the RF\_IN Pin (Pin 16). For AKMU5LP, this power source is inputted from Pin 19 VS\_AA, which is designed to route the power to RF\_IN Pin.

To power the active antenna through module's own power supply, please add an additional 10 ohm resistor between Pin18 VS\_LNA and Pin19 VS\_AA, which also enables the Antenna Advisor function such as open and short circuit detection and protection.

#### Note:

- 1. Ferrite bead L1 is added for power noise reduction.

- C1, C2, C3, and C4, decoupling capacitor should be put near the module. For C2, the value chosen depends on the amount of system noise, the range from 1uF to 100uF is reasonable.

- 3. Damping resistors R1, R2, R3, R4 and R5 could be modified based on system application.

- 4. An additional resistor R6 (10ohm) is used to connect Pin 19 VS\_LNA with Pin 18 VS\_AA, which also enables "Antenna Advisor" mechanism.

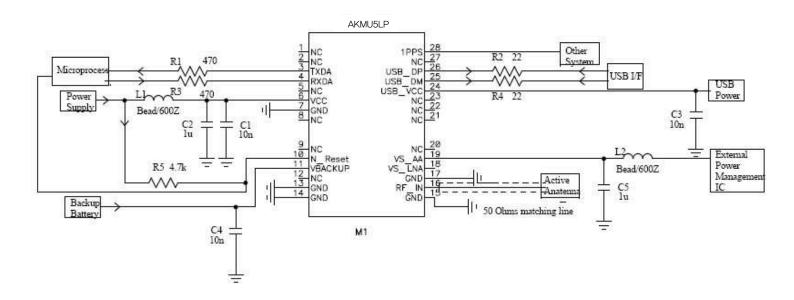

#### Active Antenna with External Power Management IC

The reference design is for those who want to use a power management IC to perform external antenna status detection by defining their own behavior. The power IC should supply power to Pin 19 VS\_AA (Range 3.0V to 3.6V, 3mA  $\langle$  current  $\langle$  30mA), which will be routed to Pin 16 RF\_IN internally, and this in turn will supply the power to the active antenna. (There is an internal inductor between VS\_AA and RF\_IN).

#### Note:

- 1. Ferrite bead L1 and L2 are added for power noise reduction.

- C1, C2, C3 and C4 decoupling capacitor should be put near the module. For C2 and C5 the value chosen depends on the amount of system noise, the range from 1uF to 100uF is reasonable.

- 3. Damping resistors R1, R2, R3, R4 and R5 could be modified based on system application.

- 4. "Antenna Advisor" mechanism will be not operational when using this design

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

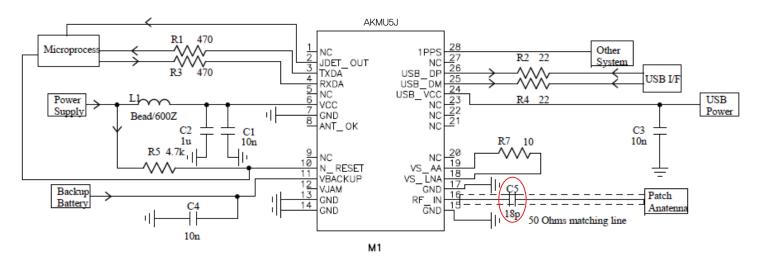

# 3.7 AKMU5J

# Patch (Passive) Antenna

When using a passive antenna, please connect the antenna directly to Pin16, RF\_IN.

Note:

- 4. The maximum Jammer detection distance: 2m or less (jamming detector @ high sensitivity)

- 5. It is not recommended to set jamming detector @ low sensitivity setting using patch antenna

- 6. If you need more support and information on antenna implementation, please directly contact us at sales@ascen.co.kr for further services.

- 7. Ferrite bead L1 is added for power noise reduction.

- 8. C5 coupling capacitor should be put near the Antenna.

- 9. C1, C2, C3 and C4 decoupling capacitor should be put near the module. For C2, the value chosen depends on the amount of system noise, the range from 1uF to 100uF

- is reasonable.

- 10. Damping resistors R1, R2, R3, R4 and R5 could be modified based on system application.

- 11. An additional resistor R7 (10ohm) is used to connect Pin 19 VS\_LNA with Pin 18 VS\_AA, which also enables "Antenna Advisor" mechanism.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc.

Rm. 710, 7F, Halla Sigma Velley B/D Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

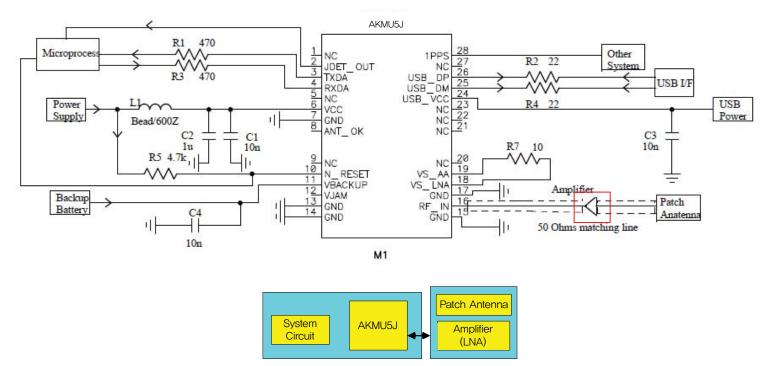

#### Patch (Passive) Antenna (additional stage LNA)

#### Adding a LNA between Patch Antenna and RF\_IN pin will increase jamming detection distance.

When using a passive antenna, please connect the antenna directly to Pin16, RF\_IN.

Reference System Block Diagram

#### Note:

- 1. Addition Amplifier (LNA: Gain (20dB, NF (2dB) between RF\_IN pin and Passive (Patch) Antenna will increase GPS jammer detection distance. Recommended Component: JRC NJG1107HB3

- 2. Patch Antenna + LNA must be placed directly before AKMU5J RF-end (RF\_IN). This is to prevent the accidental detection of internal system interference. No additional spacing is required between the antenna and RF\_IN pin.

- 3. Patch Antenna + LNA must not be placed at the opposite side of PCB from AKMU5J

- 4. Power supply for LNA will be directly provided by RF\_IN pin. The voltage range is 3V~3.6V.

- 5. If you need more support and information on antenna implementation, please directly contact us at sales@ascen.co.kr for further services.

- 6. Ferrite bead L1 is added for power noise reduction.

- 7. C5 coupling capacitor should be put near the Antenna.

- C1, C2, C3, and C4 decoupling capacitor should be put near the module. For C2, the value chosen depends on the amount of system noise, the range from 1uF to 100uF is reasonable.

- 9. Damping resistors R1, R2, R3, R4 and R5 could be modified based on system application.

- 10. An additional resistor R7 (10ohm) is used to connect Pin 19 VS\_LNA with Pin 18 VS\_AA, which also enables "Antenna Advisor" mechanism.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

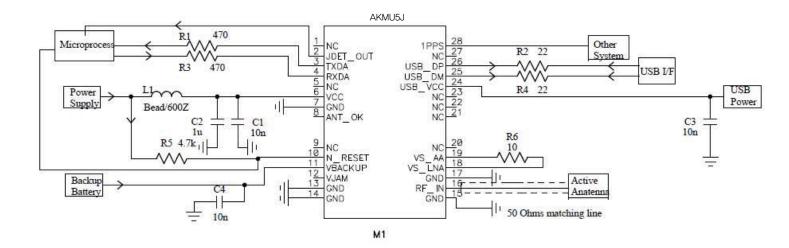

## Active Antenna with Antenna Advisor

When using an active antenna, a supply voltage is typically required to drive the internal LNA located inside the active antenna. For majority of the active antenna, the power will be sent on the same coaxial cable used for GPS signal reception through the RF\_IN Pin (Pin 16). For AKMU5J, this power source is inputted from Pin 19 VS\_AA, which is designed to route the power to RF\_IN Pin.

To power the active antenna through module's own power supply, please add an additional 10 ohm resistor between Pin18 VS\_LNA and Pin19 VS\_AA, which also enables the Antenna Advisor function such as open and short circuit detection and protection.

## Note:

- 5. Please refer to Chapter 4.6 for maximum GPS jammer detection distance.

- 6. If you need more support and information on antenna implementation, please directly contact us at sales@ascen.co.kr for further services.

- 7. Ferrite bead L1 is added for power noise reduction.

- C1, C2, C3 and C4 decoupling capacitor should be put near the module. For C2, the value chosen depends on the amount of system noise, the range from 1uF to 100uF is reasonable.

- 9. Damping resistors R1, R2, R3, R4, and R5 could be modified based on system application.

- 10. An additional resistor R6 (10ohm) is used to connect Pin 19 VS\_LNA with Pin 18 VS\_AA, which also enables "Antenna Advisor" mechanism.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc.

Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

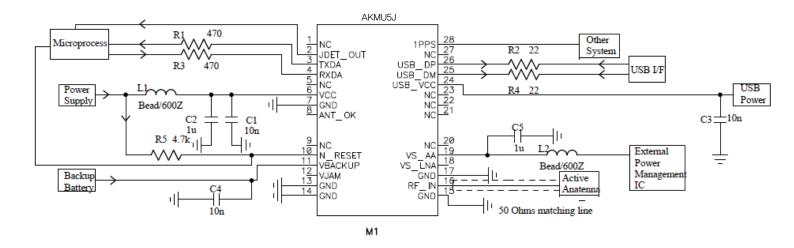

## Active Antenna with External Power Management IC

The reference design is for those who want to use a power management IC to perform external antenna status detection by defining their own behavior. The power IC should supply power to Pin 19 VS\_AA (Range 3.0V to 3.6V, 3mA  $\langle$  current  $\langle$  30mA), which will be routed to Pin 16 RF\_IN internally, and this in turn will supply the power to the active antenna. (There is an internal inductor between VS\_AA and RF\_IN).

### Note:

- 5. Please refer to Chapter 4.6 for maximum GPS jammer detection distance.

- 6. If you need more support and information on antenna implementation, please directly contact us at sales@ascen.co.kr for further services.

- 7. Ferrite bead L1 and L2 are added for power noise reduction.

- C1, C2, C3, C4 and C5 decoupling capacitor should be put near the module. For C2 and C5 the value chosen depends on the amount of system noise, the range from 1uF to 100uF is reasonable.

- 9. Damping resistors R1, R2, R3, R4 and R5 could be modified based on system application.

- 10. "Antenna Advisor" mechanism will be not operational when using this design.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/O Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

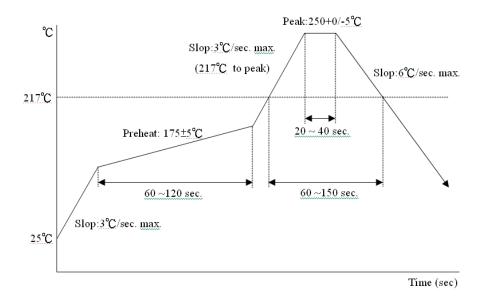

# 4. Thermal Profile for SMD Modules

# (Reference Only)

\*All the information in this sheet should be used only for Pb-free certification. SMT Reflow Soldering Temperature Profile:

Average ramp-up rate  $(25 \sim 150^{\circ} \text{ C})$ : 3° C/sec. max. Average ramp-up rate  $(270^{\circ} \text{ C to peak})$ : 3° C/sec. max. Preheat: 175 ± 25° C ′ 60 ~ 120 seconds Temperature maintained above 217° C: 60~150 seconds Peak temperature: 250 +0/-5° C′ 20~40 seconds Ramp-down rate: 6° C/sec. max. Time 25° C to peak temperature: 8 minutes max.

### SMT Solder Mask:

Please use the dimension of PCB pad as reference and shrink the size by 0.1 to 0.2 mm and use that as layout for paste mask. (For PCB pad layout, please see "Recommended PCB pad layout" on individual GPS module data sheet)

### Manual Soldering:

Soldering iron: Bit Temperature: Under 380° C

Time: Under 3 second.

# 5. Troubleshooting

## How to check for the working status of AKS6/AKS6B?

The first thing to check for is the NMEA sentence output through TX by using various application tools. For example: you can use windows default tool – WinXP Hyperterminal, or you can use other GPS application program to check for GPS status.

If there is no NMEA output, this indicates the PA6/PA6B module is currently not working. Please double check your schematic design. Down below we listed some of the possible items to check for your reference:

## Item 1: VCC (Pin1)

The voltage should be kept between 3.2V to 5.0V. (Typical : 3.3V), Please double-check.

## Item 2: ENABLE (Pin2)

AKS6/AKS6B module have internal resistor to pull high (to Vcc), the level is Vcc level, please check the enable pin should be kept between 3.2V to 5.0V. (Typical : 3.3V), Please double-check.

### Item 3: VBACKUP (Pin4)

The voltage should be kept between  $2.0V \sim 4.3V$ . (Typical : 3.0V). If the module has no power for the VBACKUP, the GPS module will not work. It is recommended that a sustain power for VBACUP is supplied to keep RTC time and navigation data, Please double-check

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

Ascenkorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.Ascenkorea.com /sales@ascen.co.kr

copyright (c) AscenKorea Inc. All right reserved

# Item 4: 3D-FIX (Pin5)

If all the measurements are within the specifications, please also measure 3D–FIX (Pin5) signal. Before 2D Fix, the pin should output one-second high-level signal follow with one-second low-level signal.

# TXD (Pin9)

The UART transmitter of the module, it outputs the GPS NMEA information for application.

1 1.00V/ 500g/ Stop Pat1 1.44V 1.89s  $\Delta X = 1.00s$  $1/\Delta X = 1.0000 Hz$  $\Delta Y(1) =$ 2.81V Source X2 2.99s Mode X X1 1.99s Υ U X1 X2 Norma

# 6. Contact

For help or further information, please contact us via the following methods:

# Ascenkorea Technology Inc.

Address: AscenKorea Inc.

Rm. 710, 7F, Halla Sigma Valley B/D, GasanDigital 2Ro 53, Geumcheon-gu, Seoul, Korea

Tel: +82 2 858 7810 Fax: +82 2 858 7813

Web Site : www.AscenKorea.com

Sales Email: sales@ascen.co.kr

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr

# **Appendix I: Super Capacitor Design**

### About Super Capacitors

Super capacitors have a useful life-time similar to aluminum electrolytic capacitors. The life of a super capacitors capacitor is largely dependent on the operating temperature, humidity, applied voltage, current and backup time requirements. Therefore, the life of a super capacitor is determined based on the backup time set by the customer.

### How to calculate the backup time

The example below teaches how to calculate the backup time.

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea.Inc. All right reserved

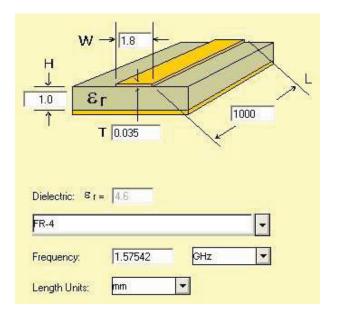

# **Appendix II: About 50 ohm Matching Line**

We used AppCAD tool for 50 ohm impedance calculation of RF line and made a table for layout reference.

| RF line width | PCB FR4   | Dielectric | Copper    |

|---------------|-----------|------------|-----------|

| (W)           | Thickness | parameter  | Thickness |

|               | (H)       |            | an ounce  |

| 1.8mm         | 1mm       | 4.6        | 0.035mm   |

Notice:

For multiple–layer layout, designer could place a ground layer in 2nd layer to minimize the trace width in specific PCB (such FR4) and impedance.

For impedance calculation, free software to cal trace width or impedance available.

Please refer to the website for one such software:

http://web.awrcorp.com/Usa/Products/Optional-Products/TX-Line/

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D, Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea Inc. All right reserved

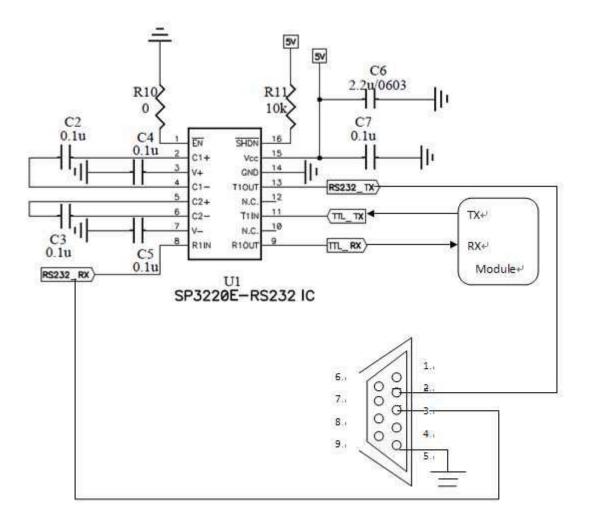

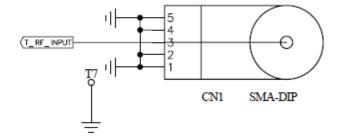

# **Appendix III: UART to RS232 Interface**

Typically RS232 or USB interface is required to connect AscenKorea Inc. GPS module directly to the PC for communication. Majority of AscenKorea Inc. modules uses a set of communication port in TTL–logic (and a newer ones have support for direct USB connection) and a bridge IC is needed for conversion to RS232 level.

Please note the supported baud-rates are: 4800, 9600, 14400, 19200, 38400, 57600, and 115200 bps.

Please refer to the reference circuits below for such conversion: (using SP3320 IC as an example)

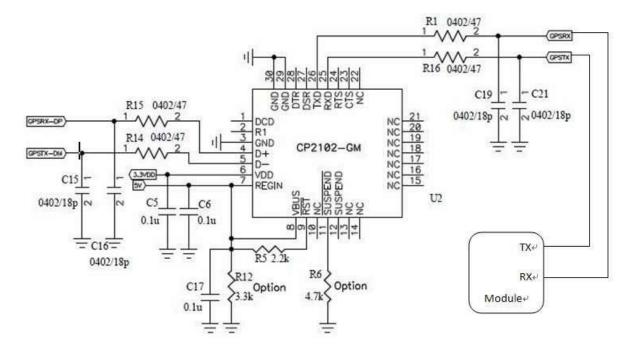

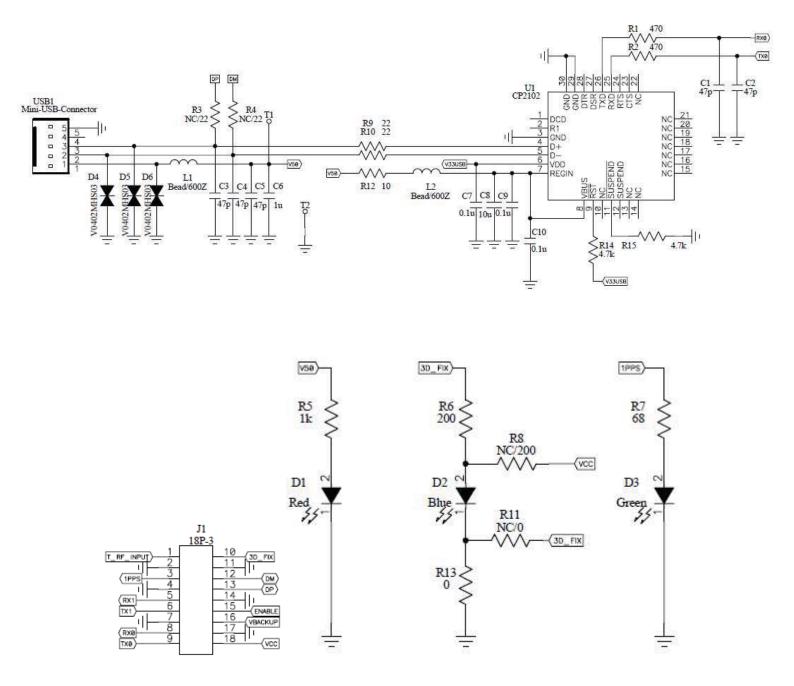

# **Appendix IV: UART to USB Interface**

If the AscenKorea Inc. module you have chosen does not contain USB interface or if you do not wish to use the integrated USB interface (perhaps due to driver or other concerns), it is possible to connect it to an external USB IC and further enhance the transferring speed by using a one capable of USB 2.0 interface. Once the driver for the chosen USB Bridge IC is successfully installed for Windows or other operating system, the USB Bridge IC will be automatically recognized as a com port within the operating system.

Note: proper driver must be installed or else the operating system will not be able to recognize the device!

Please refer to the reference circuits below for such conversion: (using CP2102 IC as an example)

(The Pin29 and Pin30 are the bottom ground pads which not be listed in IC data sheet, customer could create the decal omitted this 2 pin)

# Appendix V: How to efficiently transfer 1PPS through extended distances

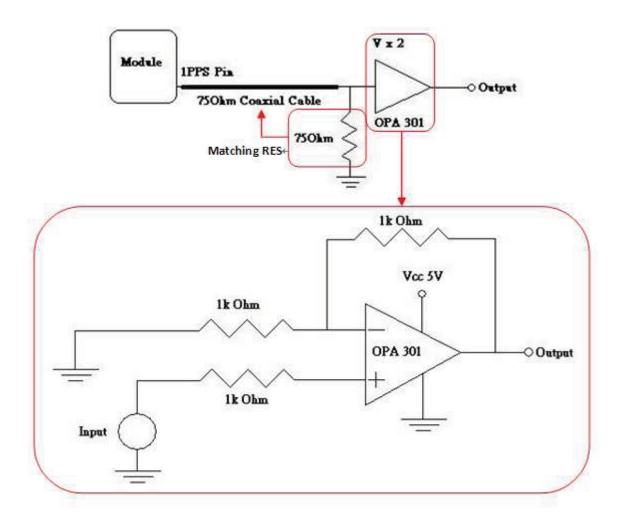

There are several things to watch out for when transferring 1PPS through long distances which will result in 1PPS signal degradation, noise and delays if proper attentions are not being paid. As the 1PPS signal passes through the communication cable, matching resistance must be implemented to prevent wave form distortions. Depending on user's application, OPA can be added to effectively control the accuracy of the voltage level determination for the 1PPS signal.

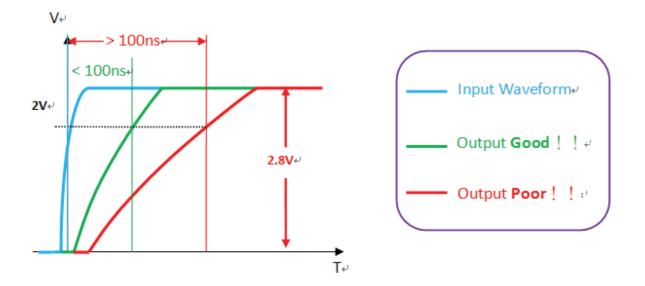

When using 1PPS signal to synchronize time, the OPA chosen should have a high slew rate property to prevent large delay in the 1PPS. The accuracy level of 1PPS for AscenKorea GPS module is within 100ns (same for majority of MTK GPS modules). The reference design below can help improving this accuracy to within 80ns.

## 1PPS Delay Time :

Specifications of AscenKorea Inc. GPS modules call for a drift error within  $\pm 100$ ns, which the design below will help to accomplish.

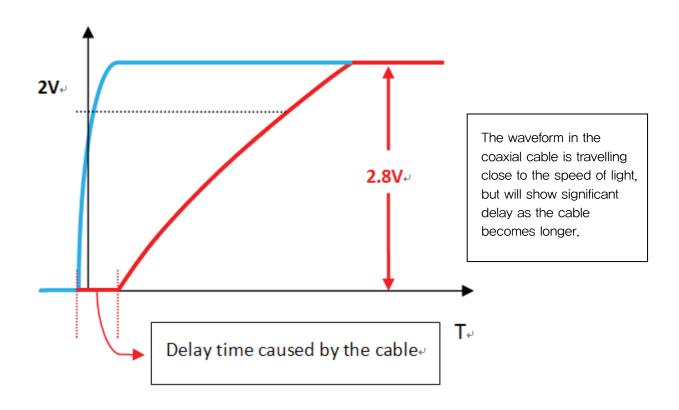

When using coaxial cable for long distances communication using OPA amplification, please pay close attention on the time delay caused by the coaxial cable and rising time of the wave form affected by OPA' s SR. A brief explanation for this is provided below:

This document is the exclusive property of AscenKorea Inc. and should not be distributed, reproduced, into any other format without prior permission of AscenKorea Inc. Specifications subject to change without prior notice.

AscenKorea Inc. Rm. 710, 7F, Halla Sigma Velley B/D Gasandigital 2Ro 53, Geumcheon-gu, Seoul, Korea Tel: +82 02 858 7810 Fax: +82 02 858 7813/ www.AscenKorea.com /sales@ascen.co.kr copyright © AscenKorea Inc. All right reserved

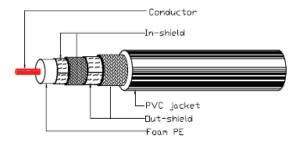

The model number for the coaxial cable is RG6U, where the figure below shows its specification.

# CONSTRUCTION